当前位置:网站首页>Introduction of modules (block, module)

Introduction of modules (block, module)

2022-07-19 03:42:00 【Small diamond wind on Shituo mountain】

Catalog

Data types and their constants and variables

Module structure

Module composition : One part describes the interface ( Port definition 、I/O explain 、 The internal signal says ), The other part describes the logic function ( Function definition ).

When referencing a module , Port connection mode :

1. Module name ( Connection port 1 Signal name , Connection port 2 Signal name ……)

2. Module name (. port 1 name ( Connecting signals 1 name ),. port 2 name ( Connecting signals 2 name )

/*I/O The description can also be in the Port declaration statement */

module module_name(input port1,input port2,……

output port1,output port2……);The internal signal says

reg [width-1:0] R Variable 1,R Variable 2……;

wire [width-1:0] W Variable 1,W Variable 2……;Function definition

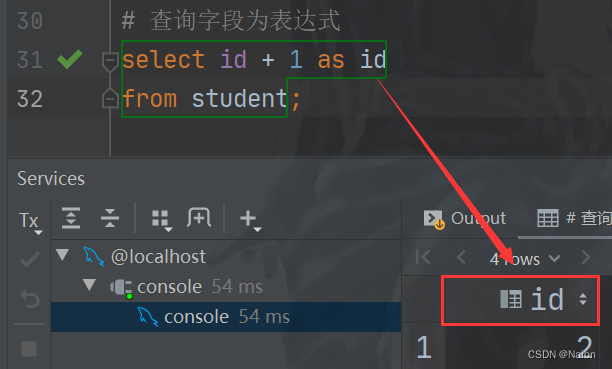

1. use assign Statement The variable can be reg( Is it because of the continuous assignment statement of the procedure ), Commonly used in combinatorial logic

2. Using example components The module referenced by the instance , Ports can be connected to the corresponding inputs of other modules through connections with different names or register type variables 、 Output signal terminal

3. always block The variable needs to be reg The statements in the block are sequential statements , Sequential execution , So we call this kind of block Process block ( It can describe combinatorial logic , It can also describe temporal logic )

/*verilog All process blocks in the module ( Such as always、initial block )、 Continuous assignment statement 、 Instance references are parallel */

assign a=b&c; //assign

and #2 u1(q,a,b); // Instance component

/* Asynchronous reset , The reset signal is the trigger signal , No matter what the clock signal is , Can be reset ; Synchronous reset , Only the clock signal is the trigger signal , Only when a certain clock triggers , Reset will happen */

[email protected](posege clk or posedge clr) //always block

begin

if (clr) q<=0;

else if (en) q<=d;

endData types and their constants and variables

Constant ( An amount that cannot be changed )

Numbers

1. Integers

The way of expression :

< A wide >< Base number >< Numbers > Comprehensive description The bit width indicates the exact number of digits of a number , The width of a binary bit is 1, One individual 16 The hexadecimal bit width is 4 8‘ha2

< Base number >< Numbers > The digital bit width adopts the default bit width ( The machine system decides , At least 32 position )

< Numbers > Use default base ( Decimal system )

2.x and z(?) value One x It can represent a binary , octal 、 Hexadecimal

3. negative Put a minus sign at the beginning of the expression

4. Underline Separation improves readability 8’b_0011_1010

Parameters (parameter) type

Constants in the form of identifiers It is often used to define delay time and variable width

parameter Width=1,Polarity=1

/* adopt #(n,n) Change parameters */

Decode #(4,0) D1(A4,F16) // The parameter changes to 4,0

Decode #(5) D2(A5,F32) // The parameter changes to 5,1

/* When changing the parameters of another module in one module , Need to use defparam command */Variable

wire

Network data type (wire、tri type ), Can't store values . If not connected to the drive ( Such as door or continuous assignment statement assign), Then the variable is in the high resistance state .wire It is usually used to represent a single door drive or continuous assignment ,tri Type variable is used to represent the network data type driven by multiple drivers . If logic strength is not defined , Under multiple driving sources , Logical values will conflict 、 Thus, an uncertain value is generated .

verilog Enter... In the program module 、 The output signal type is automatically defined as... By default wire type .wire It can be used as input to any equation , Can also be used as assign And the output of instance components .

The module referenced by the instance , Its port can be connected to the corresponding input of other modules through different connection lines or register type variables 、 Output signal terminal .

reg

Abstraction of data storage unit , Register data type .reg The default initial value is an indefinite value x, Often represents a trigger .always Each signal assigned in the module must be defined as reg, It only means that the defined signal is used in always In module , Not to say that reg Type a signal must be the output of a register or trigger .

about reg Type data , The function of the assignment statement is like changing the value of the storage unit of a group of triggers .reg When type data is an operand in an expression , Its value is treated as an unsigned value , It's a positive value . If the start register is assigned a value -1, The value in the expression is considered 15.

memory type

By expanding reg The address range of the data type is generated .

reg [7:0] mema [255:0] //256 individual 8 Bit register , Address range is 0 To 255

reg [n-1:0] rega; // One n Bit register rega=0;// legal

reg mema [n-1:0]; // One by n A memory composed of one bit registers mema=0; // illegal

Operators and expressions

Basic arithmetic operators

<= When used as a comparison operator, it is binocular operation , When used as blocking assignment, it is monocular operation , Only on the right is the operand .

An operator

Bitwise XOR (^)x And any value XOR is x; It is the same as or (^~) Is prior XOR , Reverse later .

Bit operations of different lengths , The system will automatically align the right ends of the two .

边栏推荐

- Leetcode: subsequence problem in dynamic programming

- leetcode162. Looking for peak

- Chapter 4 用户数据分析

- Thinkphp5.0模型操作使用page进行分页

- 10. Redis 面试常见问答

- central limit theorem

- Derivation of PCA principal component analysis (dimension reduction) process

- Zabbix6.0 monitoring vcenter7.0

- MySQL create project R & D account

- Laravel's problem

猜你喜欢

Chapter II linear table

MySQL 增删查改(基础)

IEEE754 standard floating point format

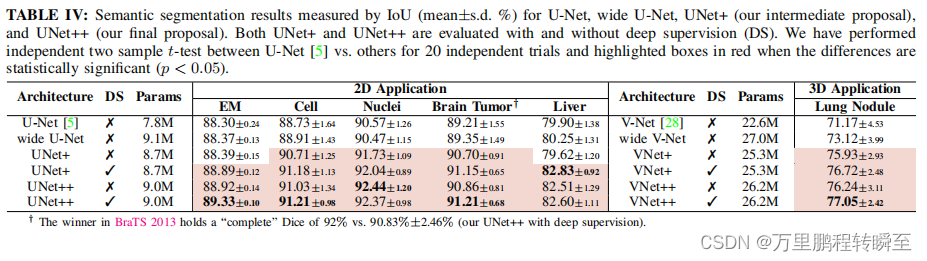

論文閱讀:U-Net++: Redesigning Skip Connections to Exploit Multiscale Features in Image Segmentation

374. Guess the size of numbers (must be able to get started)

基于MFC如何实现单个文档的文件读写

通过Dao投票STI的销毁,SeekTiger真正做到由社区驱动

Properties of Gaussian distribution (including code)

Rhce8 Study Guide Chapter 2 use of basic commands

Powertor500t reports an error 0x01806803

随机推荐

Browser cannot open tensorboard

基于Matlab的男女声音信号分析与处理

第二章 线性表

SparkCore核心设计:RDD,220716,

Machine learning library scikit learn (linear model, ridge regression, insert a column of data, extract the required column, vector machine (SVM), clustering)

leetcode 222. Number of nodes of a complete binary tree (required)

ES6 learning notes - brother Ma at station B

Oracle closes the recycle bin

Rhce8 Learning Guide Chapter 1 installing rhel8.4

Go语言中的Iota关键字怎么使用

Work fishing clock simulator wechat applet source code

Agent mode - power node of station B

oracle 查询非自增长分区的最大分区

leetcode:78. 子集

Digital type processing and convenient method of ext JS

Matlab在线性代数中的应用

oracle 关闭回收站

RuntimeError_ Input type (torch.FloatTensor) and weight type (torch.cuda.FloatTensor)

Chengxin University envi_ The second week of IDL experiment content: extract aod+ in all MODIS aerosol products for detailed analysis

ES6學習筆記——B站小馬哥