当前位置:网站首页>Allegro design entry CIS and OrCAD capture CIS relationship

Allegro design entry CIS and OrCAD capture CIS relationship

2022-07-19 02:02:00 【Hardware dog】

Cadence( Corporate name ), The company is in EDA The field is in an international leading position , its PCB Design The field is well known in the market OrCAD and Allegro SPB Two brands , among OrCAD by 90 The acquisition of brands in the s ,Allegro SPB For its Private brand , Earlier versions were called Allegro PSD. After more than ten years of integration , at present Cadence PCB The field still implements double Brand strategy ,OrCAD Covering the middle and low-end market ( Easy to use tools can be obtained at a very low price , Mainly with Protel and Pads competition ),Allegro SPB Covering medium and high-end markets ( And Mentor and Zuken competition )

OrCAD The brand covers schematic tools OrCAD Capture/Capture CIS( Contains the function of component library management ), Schematic simulation tool PSpice(PSpiceAD、PSpiceAA),PCB Layout Tools OrCAD PCB Editor(Allegro L edition ,OrCAD Originally owned OrCAD Layout stay 08 Sales have stopped worldwide since ), Signal integrity analysis tool OrCAD Signal Explorer(Allegro SI The basic version of ).

Allegro SPB The brand covers schematic tools Design Entry CIS( And OrCAD Capture CIS Exactly the same ),Concept HDL(Cadence Own schematic tools ), Schematic simulation tool Allegro AMS Simulator( namely PSpiceAD、PSpiceAA),PCB Layout Tools Allegro PCB Editor( Yes L、Performance、XL、GXL edition ). Signal integrity analysis tool Allegro PCB SI( Yes L、Performance、XL、GXL edition ).

Allegro Available products include L、XL and GXL Three levels .

Allegro L The product line is PCB Design provides products aimed at solving mainstream design problems .Allegro XL The product family drives automatic control through integrated constraints and designs production capacity based on distributed teams , Provide advanced solutions to more complex and high-end design challenges PCB Design products . Allegro GXL The product line offers differentiated PCB Design products , It can cope with advanced packaging collaborative design and thousands of MHz signal integrity (SI) Cutting edge design challenges of analysis .

Allegro Design Workbench XL It's a brand new product , for Allegro Design library provides component information and library management , It can automate the revision control of the Library , And provide the release including consistency information to the company design centers all over the world, such as RoHS Methods of known libraries . This can reduce the design cycle and component search by 50%.

“ I admit that we need to manage our processes as efficiently as we manage our data .” Senior manager of design automation of Fujitsu network communication Gary Carter Say ,“Cadence Of Allegro Design Workbench Let us achieve these two points . It can meet our process and standards after simple setting , send Cadence Our technology integrates with other tools used in our design process . Our engineers also require current 、 Complete component information , Including technical and business data , for example : cost 、 Lead time and availability 、 Be similar to RoHS Consistency data required for the indication of .Design Workbench Collect such information and enable engineers to see it from a regular perspective .”

Allegro Design Publisher XL Can pass through Allegro Design Entry HDL The resulting design is published in intelligent and easy to browse PDF In file . This provides a way for the design team inside and outside the company to browse the design without Cadence A simple way to design access tools .

This latest release is Allegro PCB SI A new board level bus analysis function is added , Can be shortened for example DDR2 Time of source synchronization signal verification of interfaces such as memory . Other enhancements related to the source synchronization interface include the on-chip terminator (ODT) Support for 、 Union of clocks 、 Filtered signal of bus 、 Board level customization incentive combination 、 And installation and control time report . in addition ,Allegro PCB Editor It is also enhanced to reduce the time of identifying critical Networks , These networks may have return path problems .

边栏推荐

- Switch details

- 动手学深度学习---从全连接层到卷积层篇

- 工厂方法模式随记

- Ace download address

- Show Me the Code之MXNet网络模型(三)

- Using XOR to exchange two variables is inefficient

- Mxnet network model of show me the code (III)

- 【文献阅读】MCUNet: Tiny Deep Learning on IoT Devices

- 监听浏览器返回操作-禁止返回上一页

- [literature reading] tenet: a framework for modeling tensor dataflow based on relational centric notation

猜你喜欢

Hands on deep learning - deep learning computing

uniapp打包H5 空白页面 报错 Uncaught SyntaxError: Unexpected token ‘<‘

Fair Attribute Classification through Latent Space De-biasing

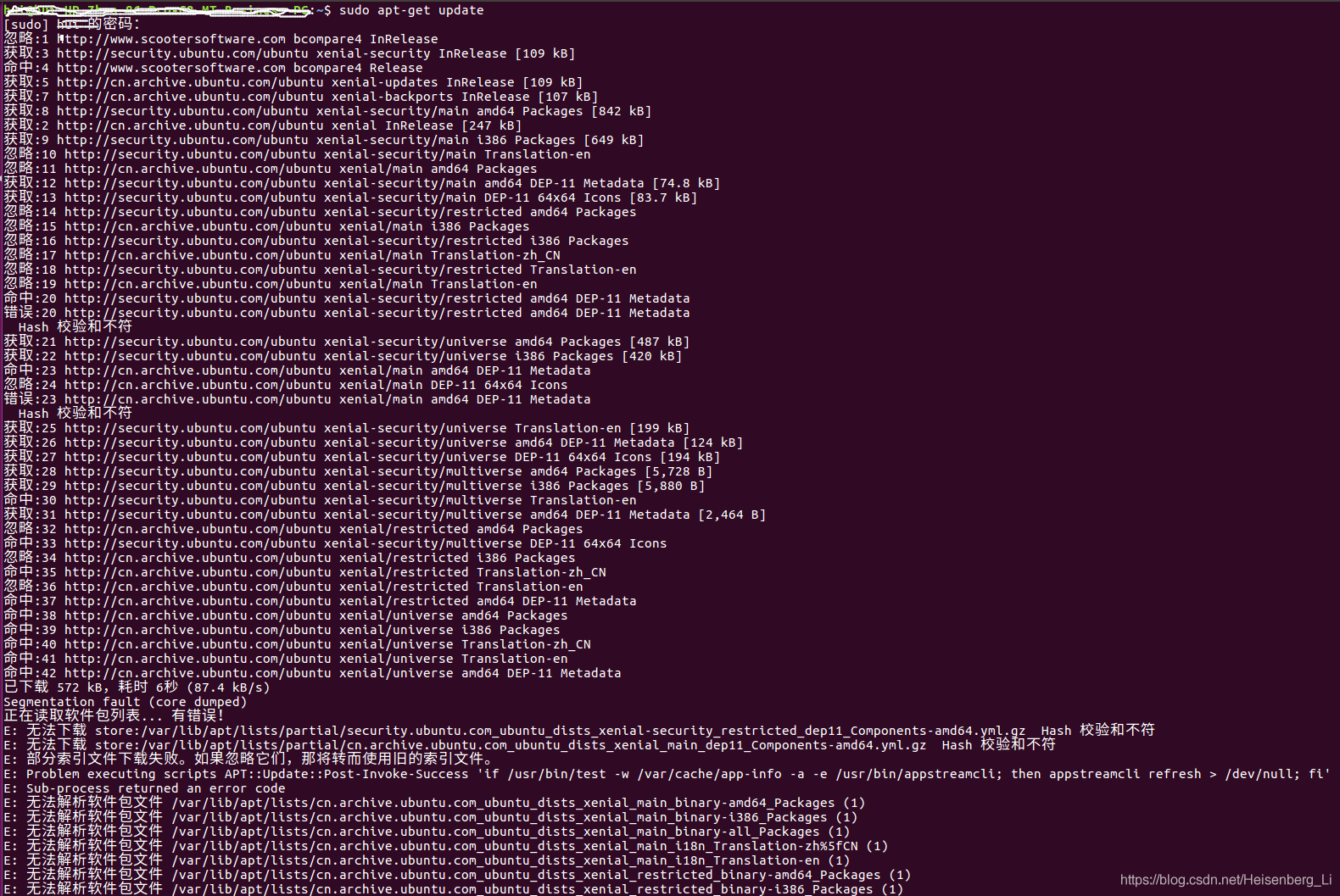

Apt get update error: hash checksum does not match

【文献阅读】Multi-state MRAM cells for hardware neuromorphic computing

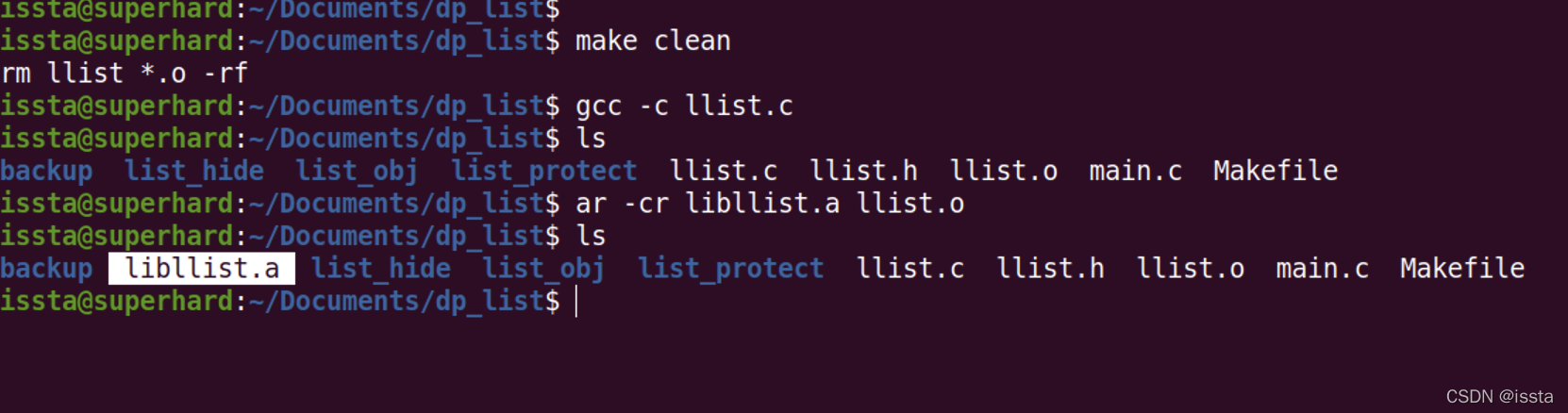

静态库与动态库

05基于ZigBee的路灯灯控故障检测系统设计

![[MySQL] windows install MySQL 5.7](/img/71/be5b0cc3e130c2b9f3884d90b9cd39.jpg)

[MySQL] windows install MySQL 5.7

Handling conditional discrimination

SAE j1708/j1587 protocol details

随机推荐

One vs One Mitigation of Intersectional Bias

【Go语言】代码覆盖测试(gcov)

[go language] detailed explanation of dynamic library and static library

Owl Eyes: Spotting UI Display Issues via Visual Understanding

【文献阅读】TENET: A Framework for Modeling Tensor Dataflow Based on Relation-centric Notation

随机森林的理解

JS tree view array batch circular operation

Using XOR to exchange two variables is inefficient

Leveraging Semi-Supervised Learning for Fairness using Neural Networks

PCA主成分分析(降维)过程推导

利用因果线性模型监测不公平A Causal Linear Model to Quantify Edge Unfairness for Unfair Edge Prioritization

Monitor browser return operation - prohibit returning to the previous page

动手学深度学习---深度学习计算篇

SAE j1708/j1587 protocol details

二階邊緣檢測 - Laplacian of Guassian 高斯拉普拉斯算子

[literature reading] isl: an integer set library for the polygonal model

组合键截图分析

01基于RFID的智能仓储管理系统设计

IGBT 直通短路过程问题分析

C语言程序之编译,链接