当前位置:网站首页>STM32 general timer

STM32 general timer

2022-07-18 14:32:00 【Three sloths】

One 、 Differences between the three timers

The timer is divided into : Advanced timer 、 General timer and basic timer

Two 、 Description of functional characteristics of general timer

STM32F4 Common to TIMx(TIM2、TIM3、TIM4 and TIM5) Timer features include :

·16/32 Position up 、 Down 、 Up / Count down mode , Auto load counter (TIMx_CNT).

·16 Bit programmable ( It can be modified in real time ) Preassigned frequency counter (TIMx_PSC), The frequency division coefficient of the counter clock frequency is 1~65535 Any number between .

·4 A separate channel (TIMx_CH1~4), These channels can be used as : Input capture 、 Output comparison 、PWM Generate ( Edge or center alignment mode )、 Monopulse mode output

· External signals can be used (TIMx_ETR) Control timer and timer Interconnection ( It can be used 1 One timer controls another timer ) The synchronous circuit of .

· The following events occur IRQ/DMA:(6 Independent IRQ/DMA Request generator )

1、 to update : Counter overflows up or down , Counter initialization ( Through software or internal / External trigger )

2、 Triggering event ( The counter starts 、 stop it 、 Initialized or internally / External trigger count )

3、 Input capture

4、 Output comparison

5、 Support for incremental positioning ( orthogonal ) Encoder and Hall sensor circuits

6、 Trigger input as an external clock or current management by cycle

·STM32 A universal timer can be used for : Measure the pulse length of the input signal ( Input capture ) Or produce an output waveform ( Output comparison and PWM) etc.

· Use a timer prescaler and RCC Clock controller prescaler , Pulse length and waveform period can be adjusted from a few microseconds to a few milliseconds .STM32 Each universal timer is completely independent , There are no resources shared with each other .

3、 ... and 、 counter mode

The general timer can count up 、 Count down 、 Up down bidirectional counting mode .

1、 Upcount mode : Counter from 0 Count to auto load value (TIMx_ARR), And then again from 0 Start counting and generate a counter overflow event .

2、 Count down mode : The counter automatically loads values from (TIMx_ARR) Start counting down to 0, Then start again with the automatically loaded values , And generate a counter down overflow event .

3、 Central counting mode ( Count up and down ): Counter from 0 Start counting to autoload value -1, Generate a counter overflow event , Then count down to 1 And generate a counter overflow event , And then from 0 Start counting again .

Four 、 General timer block diagram ( part )

General timer working process (TIM2,3,4,5)

The first part is to generate a clock ( Generation of clock source ), The second part is the actual circuit , The third part is input capture , The fourth part is output comparison , The fifth part ( middle ) Is a related register .

The main function of the first part is to produce a CK_PSC The clock , For actual circuit use .STM32 The clock sources of general timer are :1、 Internal clock (CK_INT) In fact, by APB1 A clock from frequency doubling , After reset 、 Can make 、 Up / Down 、 Count , So as to generate a clock CK_PSC, It is the first clock source .2、 External pins , Timer ETR Pin (TIMx_ETR)( Can be found in STM32F407ZGT6 Mid search ETR),ETR After polarity selection 、 Edge monitoring and prescaler , And filtering , Then trigger the controller , As the second clock source .3、ITR0~4 It is the internal trigger input port , In fact, it supports the cascade between timers ( The output of one timer can be used as the input of another timer ), Through the selector , Then trigger the controller , As the third timer .ITR The input of is from other timers TRGO.4、TI1FP1、TI2FP2, come from TI1、TI2 That is, the external channel pin of the timer . Through the selector , And trigger controller , Is the fourth clock source .

The second part is the actual circuit :CK_PSC after PSC Prescaler divides the clock , produce CK_CNT Clock as the final clock , Up according to the trigger controller / The downward setting is upward / Count down . Automatically reload the register according to the up / Set down to count accordingly ( Load the initial value from the automatic reload register ), That is, the counter mode written above .

The third part is input capture : Corresponding to each general timer , for example :TIMx_CH1 Produced TI1, Capture through input filter and edge detector , After each capture, the value of the counter should be compared to produce some time , Capture the rising edge and the falling edge respectively to know the length of time from the rising edge to the falling edge .

The fourth part is output comparison : For example, the counter counts down , Capture comparison capture a value and then compare it with the value of the comparison register , If it is greater than, a high level will be generated , Small will generate low level . This will produce high and low output levels .

Part V capture comparison : Similar to a connector , Connect the counter and input , And compare with each other and capture , Then the output .

5、 ... and 、 Selection of counting clock

The clock of the counter has 8 A choice :

1、 Inside RCC The clock provided :TIMxCLK

2、 Internal trigger input port 1~4:ITR1/ITR2/ITR3/ITR4 Use one timer as a frequency divider set by another timer

3、 External capture comparison pin : Pin 1:TI1FP1 or TI1F_ED Pin 2:TI2FP2

4、 External pins :ETR Can make / Forbidden bit Programmable polarity 4 Bit external trigger filter External trigger frequency divider : The frequency divider is off 、 Dichotomy 、 Quad frequency 、 Eight frequency division

6、 ... and 、 Time base unit

1、 Counter register (TIMx_CNT)

Count up 、 Count down or center aligned

2、 Prescaler register (TIMx_PSC)

Press the clock frequency 1~65536 Divide any value between , Its setting value can be changed during operation

3、 Auto reload register (TIMx_ARR)

If TIM1_CR1 In register ARPE Position as 0,ARR The contents of the register will be written directly to the shadow register ; If ARPE by 1,ARR The contents of the register will be updated every time UEV occurs , To the shadow register ;

If TIM1_CR1 Medium UDIS Position as 0, When the counter generates an overflow condition , Generate update event .

边栏推荐

- 自定义MVC

- Codeforces Global Round 21 C. Fishingprince Plays With Array

- [C language note sharing] custom type: structure, enumeration, Union (recommended Collection)

- Design of intelligent speech recognition Bluetooth headset based on wtk6900h speech recognition single chip

- [the most complete and detailed] seven distributed global ID generation strategies

- Kotlin | 为 Kotlin 编译器任务推出构建报告

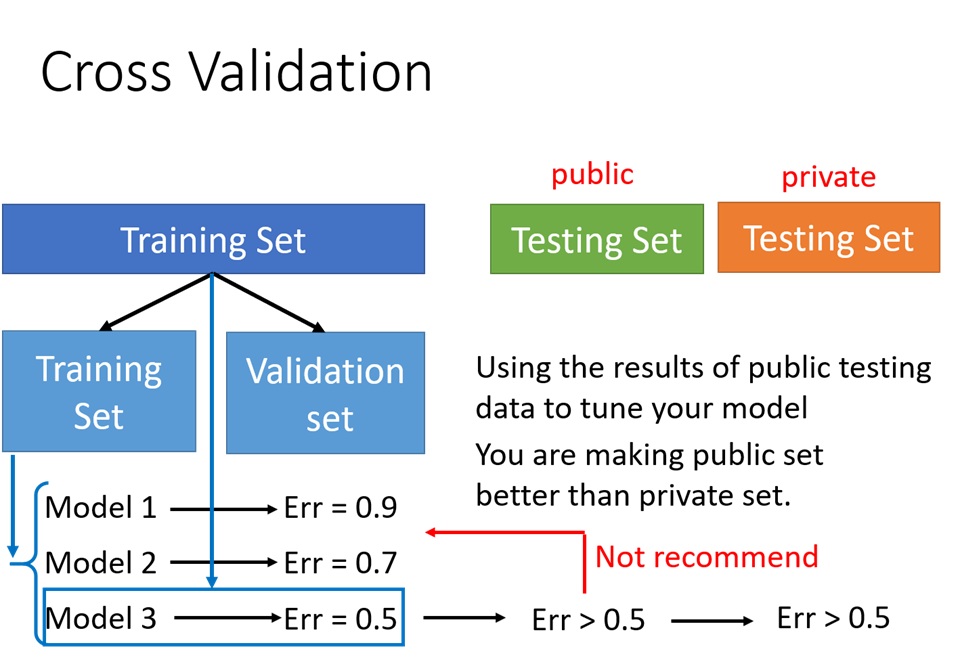

- In depth learning (2020 Li Hongyi) learning records

- Huawei ECS cloud database creation read-only process

- Arm64 Galaxy Kirin desktop system V10 (SP1) markdown editor retext replaces typora

- C&W(Carlini & Wagner)

猜你喜欢

DataX extension vertica plug-in

【基于yolov5的图像识别】

Reconstructing the geometric form of weight space with training set

Codeforces Global Round 21 B. NIT Destroys the Universe

二進制搭建 Kubernetes

我为 TDengine “带盐”!“高价”招募出镜开发者

ARM64银河麒麟桌面系统V10(SP1) markdown编辑器 retext 顶替Typora

![[C language note sharing] custom type: structure, enumeration, Union (recommended Collection)](/img/25/4a17c260b2b506ae1224520d9b85d1.png)

[C language note sharing] custom type: structure, enumeration, Union (recommended Collection)

Libevent Library Learning (2)

In depth learning (2020 Li Hongyi) learning records

随机推荐

You may not know the function of the third parameter of setTimeout

基于单片机的可燃气烟雾系统设计(#0488)

8. A network topology is shown in the figure. Router R1 connects LAN 1 and LAN 2 through interfaces E1 and E2, router R2 through interface l0, and domain name server and Internet through router R2. Th

Codeforces Global Round 21 A. NIT orz!

Codeforces Global Round 21 C. Fishingprince Plays With Array

Codeforces Round #803 (Div. 2) D. Fixed Point Guessing

斑马888-TT不认新纸

[pytorch quantitative practice (2)]

深度学习(2020李宏毅)学习记录

[atlas quick start]

HMS core graphics and image technology shows the latest functions and application scenarios, and accelerates the construction of digital intelligence life

汇编基础-CTF

[image recognition based on yolov5]

Understanding multi bank capital system (II) -- today's homepage

Design of hydrogen monitoring system based on single chip microcomputer (0490)

Interview reply 2 (summarize the bad answers in the interview)

Signal函数大全:

刷题笔记-排序

Simple function relation

Key points for upgrading firmware of Hezhou air820ug